Sure! Here's the first part of your soft article based on the given theme, with a focus on troubleshooting and solutions for the " 10M16SAU169I7G " (likely referring to a specific microcontroller or component model).

Understanding the 10M16SAU169I7G and Common Issues

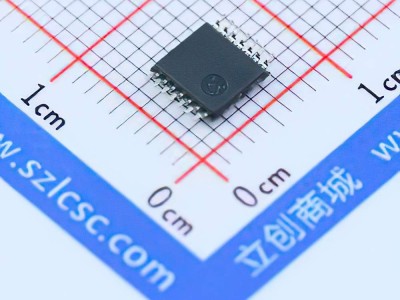

The 10M16SAU169I7G is a member of the Intel (formerly Altera) MAX 10 FPGA family, known for its versatility, low Power consumption, and efficient performance. With a focus on cost-effective designs for a wide range of applications, it’s a go-to solution for industries like automotive, industrial automation, and communications. However, like any complex technology, it’s not immune to operational challenges. Engineers often encounter various issues ranging from basic connectivity errors to more advanced configuration problems. Understanding common problems and their solutions can save time and avoid costly mistakes in your projects.

Common Troubleshooting Areas for 10M16SAU169I7G

Power Supply Problems

One of the first things to check when troubleshooting any FPGA-based system is the power supply. Inadequate or unstable power can cause a myriad of issues including unexpected resets, failure to program the device, or erratic behavior.

Symptoms: System instability, failure to initialize, or unexpected resets.

Potential Causes:

Incorrect voltage levels: Ensure the FPGA is receiving the correct supply voltage. The MAX 10 FPGAs typically require 3.3V or 1.2V depending on the I/O and core voltage configuration.

Power sequencing issues: Some FPGAs, including the 10M16SAU169I7G, may require a specific power-up sequence. Check the datasheet for power-up and power-down sequencing requirements to ensure proper operation.

Power supply noise: Noise or fluctuations in the power supply can affect FPGA performance, causing erratic behavior or instability.

Solutions:

Use an oscilloscope to monitor the power rails during startup.

If noise is detected, adding decoupling capacitor s close to the power pins of the FPGA can help reduce power noise and ensure stable operation.

Double-check your power sources and ensure they meet the voltage and current requirements for the FPGA.

Programming Issues and Configuration Failures

The 10M16SAU169I7G, like other FPGAs, requires proper configuration for operation. Programming issues can arise if the FPGA is not properly configured, or if the configuration file is corrupt or incorrectly written.

Symptoms: The FPGA fails to initialize or does not function as expected after programming.

Potential Causes:

Corrupted configuration files: Ensure that the bitstream file used to configure the FPGA is correct and free of errors.

JTAG or configuration interface problems: Faulty connections in the JTAG interface or programming cable can prevent successful programming.

Incompatible Clock settings: The FPGA may fail to configure properly if the clock settings are misconfigured.

Solutions:

Verify that the bitstream file is correct, and recompile it if necessary.

Check the JTAG or configuration interface connections to ensure they are secure and properly connected to both the FPGA and programming device.

Use the built-in self-test (BIST) features of the FPGA to diagnose configuration issues.

Check for any clocking or Timing issues that may interfere with the configuration process. Ensure that the clock constraints are correctly defined in your design.

I/O Pin Configuration Issues

Misconfigured I/O pins can cause various problems in FPGA-based systems. These issues typically arise when the pin assignments are incorrect, or when the I/O voltage levels are not compatible with the external components.

Symptoms: Peripheral devices connected to the FPGA do not function correctly, or I/O pins fail to respond.

Potential Causes:

Incorrect pin assignments: Double-check that the I/O pins are correctly mapped in your design files.

Voltage level mismatch: Ensure that the voltage levels of the FPGA I/O pins match those of the connected devices.

Faulty or incorrectly connected external components: Ensure that external components are correctly wired and compatible with the FPGA I/O standards.

Solutions:

Review the pin assignments and cross-check them with your PCB layout.

Use a multimeter to check for continuity in the I/O connections.

Verify that the external components connected to the I/O pins are functioning correctly and within specification.

If necessary, adjust the I/O voltage levels or add level-shifting circuitry to ensure compatibility.

Timing and Clocking Issues

One of the most common and subtle issues that can affect FPGA performance is timing and clocking. The 10M16SAU169I7G relies on precise clocking for synchronization of its internal logic and I/O operations. Timing violations can lead to improper functionality or erratic behavior.

Symptoms: The FPGA fails to meet timing constraints, causing logic errors, or the system operates intermittently.

Potential Causes:

Incorrect clock constraints: Timing issues often arise from improperly defined clock constraints in the design files.

Clock skew: If clock signals are not properly routed or have uneven propagation times, timing errors can occur.

Insufficient timing margin: The FPGA might not meet timing requirements due to excessive logic or inadequate routing.

Solutions:

Use FPGA design software (such as Intel Quartus) to analyze timing reports and identify any violations or warnings.

Ensure that clock routing is optimized and that clock skew is minimized by following best practices for FPGA clock design.

Re-compile the design with adjusted timing constraints, and use the FPGA’s built-in tools for timing analysis.

Signal Integrity and Noise

Poor signal integrity can cause significant issues in high-speed FPGA designs. Noise on the signal lines, especially on high-speed I/O pins, can introduce errors and reduce system reliability.

Symptoms: Data corruption, communication errors, or intermittent system failures.

Potential Causes:

Crosstalk between signal lines: In densely packed designs, signal lines running close together may interfere with each other.

Reflections or impedance mismatch: Improper PCB layout or trace design can cause signal reflections, leading to data integrity problems.

Power supply noise: As mentioned earlier, noise on the power rails can also affect signal integrity.

Solutions:

Use differential signaling for high-speed data lines to reduce susceptibility to noise.

Implement proper termination techniques to minimize reflections and impedance mismatches.

Review the PCB layout to ensure that signal lines are adequately spaced and that sensitive lines are shielded from noisy signals.

Use signal integrity tools provided by FPGA development environments to analyze and optimize your design.

Advanced Troubleshooting and Solutions for the 10M16SAU169I7G

The second part of the article will focus on more advanced diagnostic techniques and in-depth solutions for issues such as debugging, firmware verification, and optimizing performance. Stay tuned as we dive into these critical troubleshooting aspects in the next section.

This is the first part of your article. If you are satisfied with it, I can continue to the second part, focusing on more advanced troubleshooting and optimization techniques for the 10M16SAU169I7G. Let me know if you'd like me to proceed!

Partnering with an electronic components supplier sets your team up for success, ensuring the design, production, and procurement processes are quality and error-free.